# Technical Manual and Data Sheet

# SC15 Wireless Media Processor

PRELIMINARY PROVIDED UNDER NDA

DP-01433-001\_v04.001

# HANDHELD

# This page left blank intentionally.

# Contents

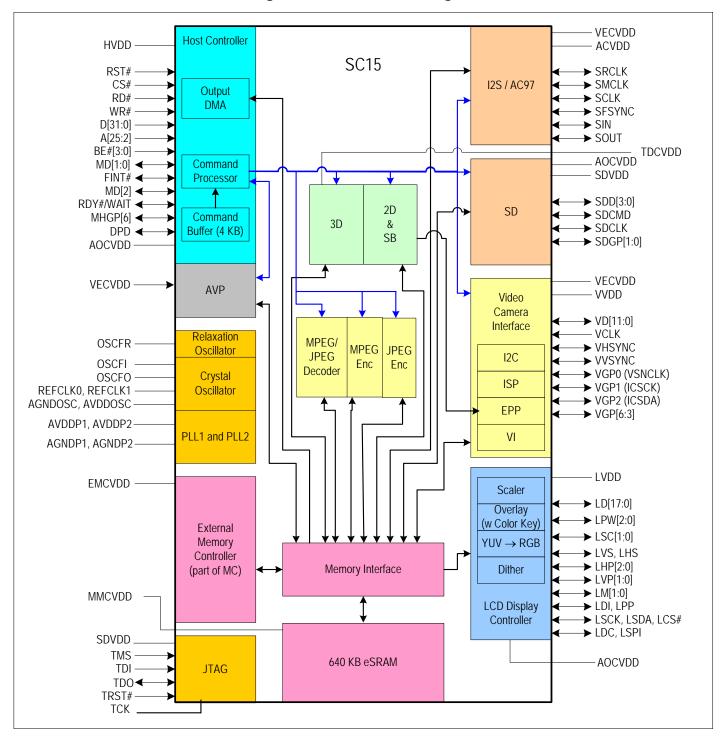

| Chapter | 1      | Overview       |                                                |

|---------|--------|----------------|------------------------------------------------|

| 1.1     | Introc | luction        |                                                |

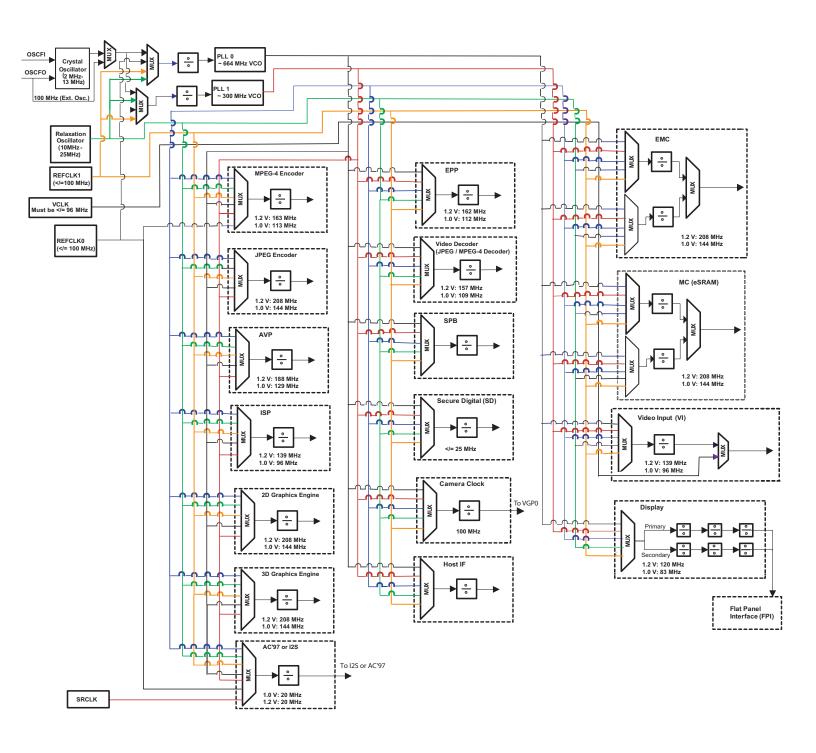

| 1.2     | Block  | Diagram        |                                                |

| 1.3     | Featu  | res            |                                                |

| Chapter | 2      | Functional     | Descriptions2-1                                |

| 2.1     | Overv  | /iew           |                                                |

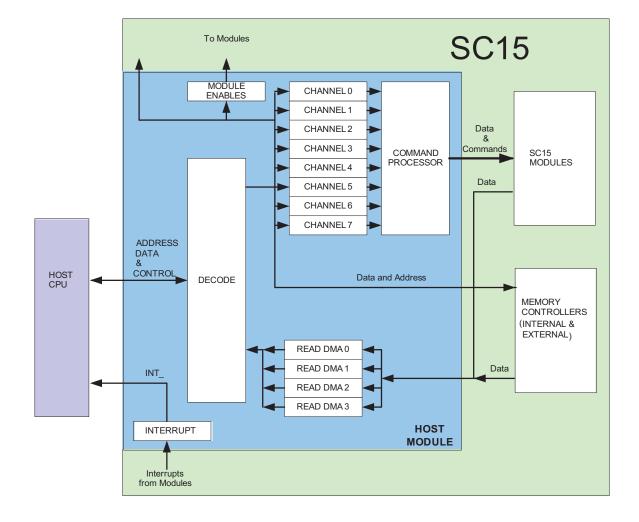

| 2.2     | Host   |                |                                                |

|         | 2.2.1  | Introducti     | on2-3                                          |

|         | 2.2.2  |                |                                                |

|         | 2.2.3  | Host Inter     | face Functional Blocks2-6                      |

|         |        | 2.2.3.1        | Interrupt / Status Control2-6                  |

|         |        | 2.2.3.2        | Module Enables2-6                              |

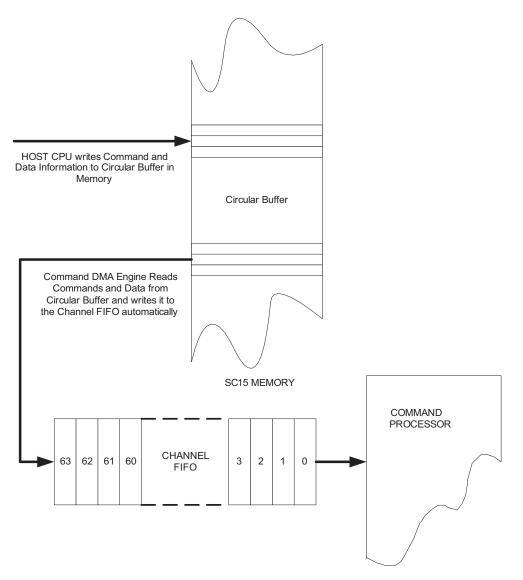

|         |        | 2.2.3.3        | Command Processor2-7                           |

|         |        | 2.2.3.4        | Command Buffer DMA2-7                          |

|         |        | 2.2.3.5        | Read DMA FIFOs2-8                              |

|         |        | 2.2.3.6        | Module Register Reads2-9                       |

|         | 2.2.4  | Host Bus I     | nterfaces2-9                                   |

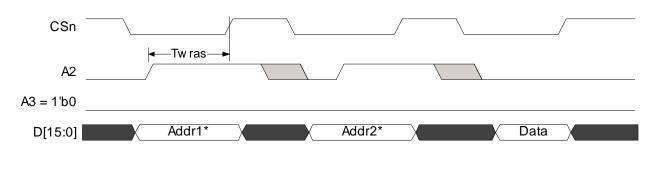

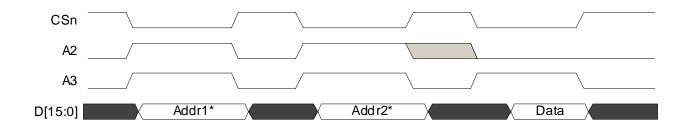

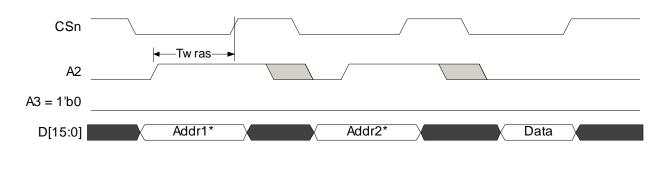

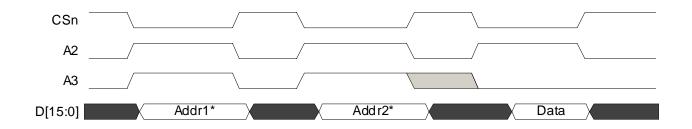

|         |        | 2.2.4.1        | Indirect Addressing Mode2-10                   |

|         |        | 2.2.4.2        | Direct Linear Addressing to Display Memory2-11 |

|         | 2.2.5  | SC15 Add       | ress Map2-11                                   |

| 2.3     | Audio  | Video Proces   | sor (AVP)2-12                                  |

| 2.5     | 2.3.1  |                | on2-12                                         |

|         | 2.3.2  |                |                                                |

| 2.4     | Memo   | orv Controller |                                                |

|         | 2.4.1  |                | on2-13                                         |

|         | 2.4.2  | Overview       |                                                |

| 2.5     | 2D En  |                |                                                |

|         | 2.5.1  | Introducti     | on2-15                                         |

|         | 2.5.2  |                |                                                |

|         | 2.5.3  | Rotation i     | 1 the 2D Engine2-17                            |

|         |        | 2.5.3.1        | Fast Rotation2-17                              |

|         | 2.5.4  | 2D Engine      | Interfaces2-18                                 |

|         | 2.5.5  | 2D Engine      | Clocks and Power Savings2-18                   |

| 2.6     | Video  | Scaler         |                                                |

|         | 2.6.1  |                | on2-19                                         |

|         | 2.6.2  |                |                                                |

|         | 2.6.3  |                | and the VS2-20                                 |

|         |        | 2.6.3.1        | Slow Rotation                                  |

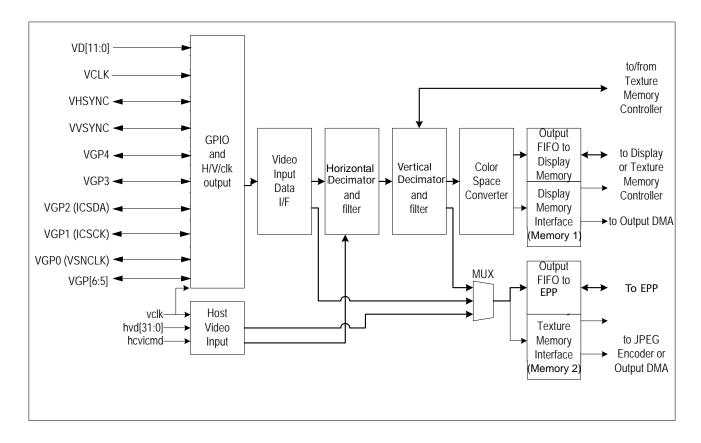

| 2.7     | Video  | Input (VI)     |                                                |

|         | 2.7.1  | •              | on2-21                                         |

|         | 2.7.2  |                |                                                |

|         | 2.7.3  |                | Block Functions                                |

|         | 2.7.5  | 2.7.3.1        | Video Signal Processing                        |

|         |        | 2.7.3.2        | VI Color-space Converter                       |

|         |        | 2.7.3.2        |                                                |

|       | 2.7.4            | VI Module Interfaces<br>2.7.4.1 Input From the Host Interface |       |  |

|-------|------------------|---------------------------------------------------------------|-------|--|

|       |                  | 2.7.4.2 VI GPIO                                               |       |  |

|       |                  | 2.7.4.3 VI Data I/F                                           |       |  |

|       |                  | 2.7.4.4 VI Output Memory Interface 1                          |       |  |

|       |                  | 2.7.4.5 Video YUV4:2:0 Write Data Format                      |       |  |

|       | 2.7.5            | Slow Rotation                                                 |       |  |

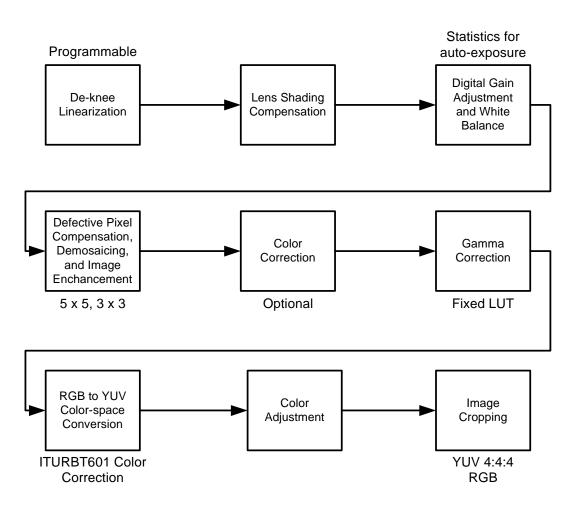

| 2.8   |                  | ignal Processor (ISP)2                                        |       |  |

| 2.0   | 2.8.1            | Introduction                                                  |       |  |

|       | 2.8.2            | Overview                                                      |       |  |

|       | 2.8.3            | ISP Functional Blocks                                         |       |  |

|       | 2.8.4            | Data Input to ISP                                             |       |  |

| 2.0   | - I              |                                                               |       |  |

| 2.9   | 2.9.1            | Pre-processor (EPP)2<br>Introduction                          |       |  |

|       | 2.9.1            | Overview                                                      |       |  |

|       | 2.9.2            | Slow Rotation                                                 | -     |  |

|       | 2.9.4            | Interfaces                                                    |       |  |

|       |                  |                                                               |       |  |

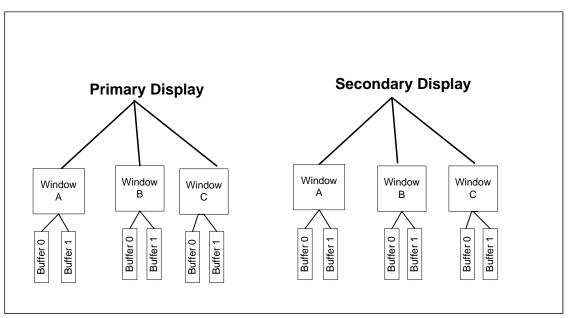

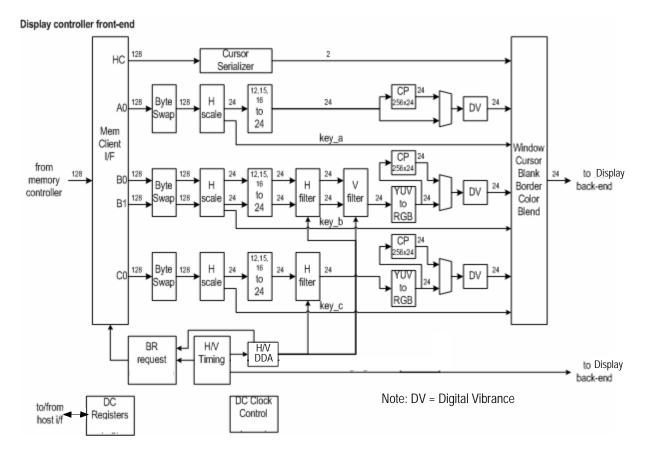

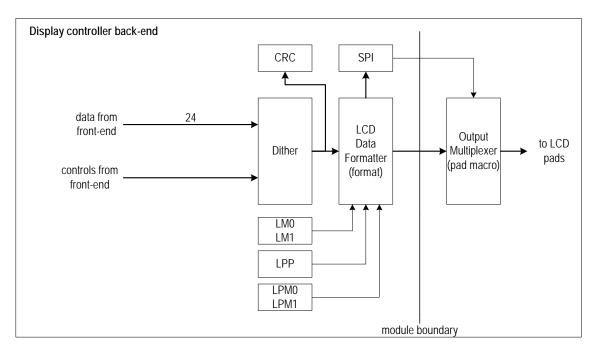

| 2.10  | • •              |                                                               |       |  |

|       | 2.10.1           | Introduction                                                  |       |  |

|       | 2.10.2           | Overview<br>Display Module Functional Blocks                  |       |  |

|       | 2.10.3           | 2.10.3.1 Output Window to EPP                                 |       |  |

|       |                  | 2.10.3.2 One shot control                                     |       |  |

|       |                  | 2.10.3.3 Color Key and Overlay Blend                          |       |  |

|       |                  | 2.10.3.4 Display Transformation                               |       |  |

|       | 2.10.4           | Display Interface to Host                                     |       |  |

|       | 2.10.5           | Pin Output Selection                                          |       |  |

| 2.11  | IPEC End         | coder                                                         | 2- 50 |  |

| 2.11  | 2.11.1           | Introduction                                                  |       |  |

|       | 2.11.2           | Overview                                                      |       |  |

| 2 1 2 |                  |                                                               |       |  |

| 2.12  |                  | Encoder                                                       |       |  |

|       | 2.12.1           | וחנרסמעכנוסה                                                  | 2-21  |  |

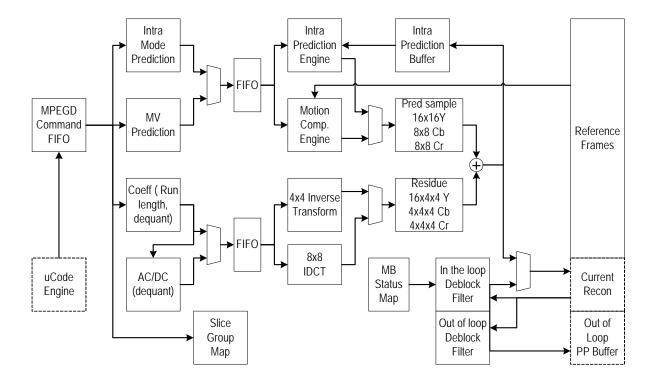

| 2.13  | Video D          | ecoder2                                                       | 2- 52 |  |

|       | 2.13.1           | Introduction                                                  |       |  |

|       |                  | MPEG-4 Decode Overview                                        |       |  |

|       | 2.13.3           | JPEG Decoder Overview                                         | 2-54  |  |

| 2.14  | 3D Grap          | phics Engine                                                  | 2- 55 |  |

|       | 2.14.1           | Introduction                                                  |       |  |

| 2.15  |                  |                                                               |       |  |

| 2.15  |                  | ed Memory2<br>Introduction                                    |       |  |

|       | 2.15.1<br>2.15.2 |                                                               |       |  |

|       |                  |                                                               |       |  |

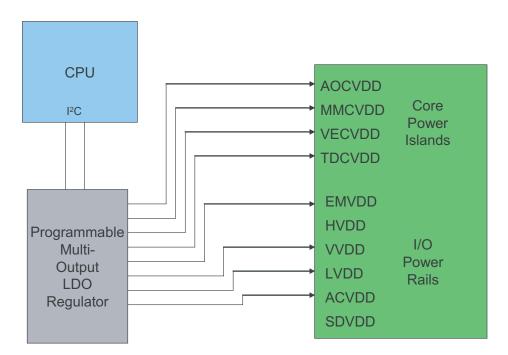

| 2.16  |                  | 1anagement2                                                   |       |  |

|       | 2.16.1           | Introduction                                                  |       |  |

|       | 2.16.2           | Overview                                                      |       |  |

|       |                  | 2.16.2.1 Power Islands                                        | 2-57  |  |

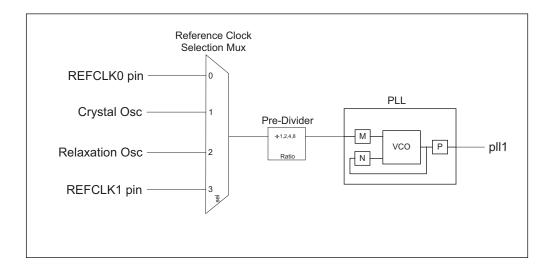

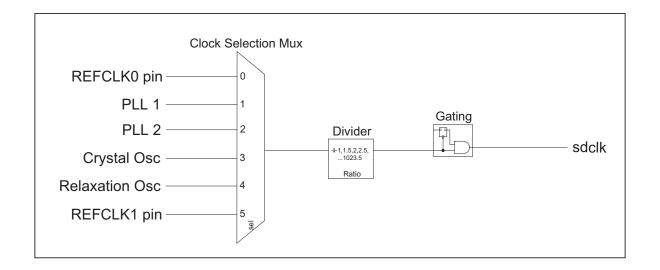

| 2.17  | 2.17 Clocks      |                                                               |       |  |

|       | 2.17.1           | Introduction                                                  | 2-58  |  |

|       | 2.17.2           | Overview                                                      |       |  |

|       | 2.17.3           | Relaxation Oscillator                                         | 2-61  |  |

|                                                                     | 2.17.3.1 Clock Distribution                                                                                                                                                                                                                                                                                                          |                                 |

|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|                                                                     | 2.17.4 PLL Frequency Calculation                                                                                                                                                                                                                                                                                                     | 2-63                            |

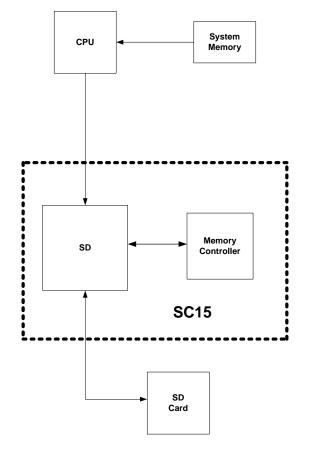

| 2.18                                                                | ( <b>- - - - - - - - -</b>                                                                                                                                                                                                                                                                                                           |                                 |

|                                                                     | 2.18.1 Introduction                                                                                                                                                                                                                                                                                                                  |                                 |

|                                                                     | 2.18.2 Overview                                                                                                                                                                                                                                                                                                                      |                                 |

|                                                                     | 2.18.3 SD Functional Blocks                                                                                                                                                                                                                                                                                                          |                                 |

|                                                                     | 2.18.3.1 Pull-up and Pull-down Resistors for CMD/DATA Lines                                                                                                                                                                                                                                                                          |                                 |

|                                                                     | 2.18.4 SD Host Transfers                                                                                                                                                                                                                                                                                                             |                                 |

|                                                                     | 2.18.5 SD Module Interfaces                                                                                                                                                                                                                                                                                                          |                                 |

|                                                                     | 2.18.5.1 Command Transfers                                                                                                                                                                                                                                                                                                           |                                 |

|                                                                     | 2.18.5.2 Data Transfers                                                                                                                                                                                                                                                                                                              |                                 |

|                                                                     | 2.18.5.3 Transmit (Write) Operation                                                                                                                                                                                                                                                                                                  |                                 |

|                                                                     | 2.18.5.4 Receive (Read) Operation                                                                                                                                                                                                                                                                                                    |                                 |

|                                                                     | 2.18.6 SD Error Recovery                                                                                                                                                                                                                                                                                                             | 2-67                            |

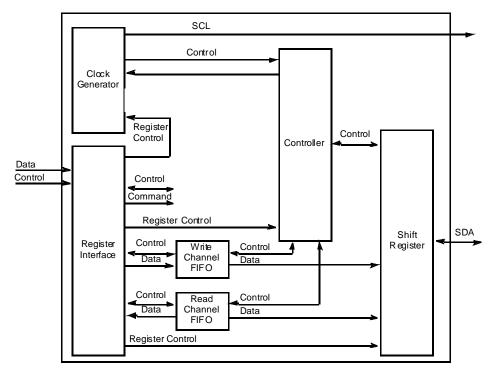

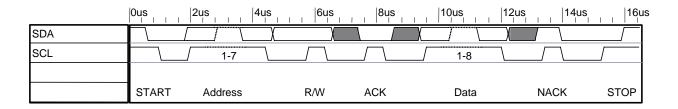

| 2.19                                                                | Serial Peripheral Bus (SPB)                                                                                                                                                                                                                                                                                                          | 2- 69                           |

|                                                                     | 2.19.1 Introduction                                                                                                                                                                                                                                                                                                                  | 2-69                            |

|                                                                     | 2.19.2 Overview                                                                                                                                                                                                                                                                                                                      | 2-70                            |

|                                                                     | 2.19.3 SPB Functional Blocks                                                                                                                                                                                                                                                                                                         | 2-70                            |

|                                                                     | 2.19.4 Clocks                                                                                                                                                                                                                                                                                                                        | 2-71                            |

| 2 20                                                                |                                                                                                                                                                                                                                                                                                                                      | 2 72                            |

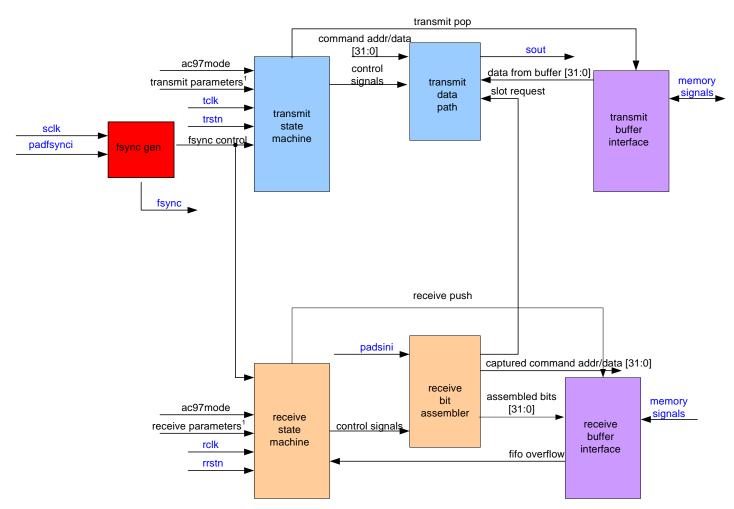

| 2.20                                                                | I2S and AC'97 Codec Interface                                                                                                                                                                                                                                                                                                        |                                 |

|                                                                     | 2.20.1 Introduction<br>2.20.2 Overview                                                                                                                                                                                                                                                                                               |                                 |

|                                                                     | 2.20.2 Overview                                                                                                                                                                                                                                                                                                                      | 2-75                            |

|                                                                     |                                                                                                                                                                                                                                                                                                                                      |                                 |

| Chantor                                                             | 43 Signals                                                                                                                                                                                                                                                                                                                           | 2.1                             |

| Chapter                                                             | <sup>•</sup> 3 Signals                                                                                                                                                                                                                                                                                                               | 3-1                             |

| Chapter<br>3.1                                                      | <sup>r</sup> 3 Signals                                                                                                                                                                                                                                                                                                               |                                 |

| 3.1                                                                 | Introduction                                                                                                                                                                                                                                                                                                                         | 3- 1                            |

| •                                                                   | -                                                                                                                                                                                                                                                                                                                                    | 3- 1                            |

| 3.1<br>3.2                                                          | Introduction<br>Pin Types and Conventions Used                                                                                                                                                                                                                                                                                       | 3- 1<br>3- 1                    |

| 3.1                                                                 | Introduction                                                                                                                                                                                                                                                                                                                         | 3- 1<br>3- 1                    |

| 3.1<br>3.2                                                          | Introduction<br>Pin Types and Conventions Used<br>Power and Ground Pins                                                                                                                                                                                                                                                              | 3- 1<br>3- 1<br>3- 2            |

| 3.1<br>3.2<br>3.3                                                   | Introduction<br>Pin Types and Conventions Used<br>Power and Ground Pins<br>SC15 I/O Power Rails                                                                                                                                                                                                                                      | 3- 1<br>3- 1<br>3- 2<br>3- 4    |

| 3.1<br>3.2<br>3.3                                                   | Introduction<br>Pin Types and Conventions Used<br>Power and Ground Pins<br>SC15 I/O Power Rails                                                                                                                                                                                                                                      | 3-1<br>3-1<br>3-2<br>3-4<br>3-4 |

| 3.1<br>3.2<br>3.3<br>3.4                                            | Introduction<br>Pin Types and Conventions Used<br>Power and Ground Pins<br>SC15 I/O Power Rails<br>3.4.1 Notes on Using the SC15 I/O Power Rails<br>3.4.1.1 Power Savings Tips                                                                                                                                                       |                                 |

| 3.1<br>3.2<br>3.3                                                   | Introduction<br>Pin Types and Conventions Used<br>Power and Ground Pins<br>SC15 I/O Power Rails<br>3.4.1 Notes on Using the SC15 I/O Power Rails                                                                                                                                                                                     |                                 |

| 3.1<br>3.2<br>3.3<br>3.4                                            | Introduction<br>Pin Types and Conventions Used<br>Power and Ground Pins<br>SC15 I/O Power Rails<br>3.4.1 Notes on Using the SC15 I/O Power Rails<br>3.4.1.1 Power Savings Tips                                                                                                                                                       |                                 |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6                              | Introduction<br>Pin Types and Conventions Used<br>Power and Ground Pins<br>SC15 I/O Power Rails<br>3.4.1 Notes on Using the SC15 I/O Power Rails<br>3.4.1.1 Power Savings Tips<br>Host Bus Interface Pins.<br>Video Input Pins                                                                                                       |                                 |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5                                     | Introduction<br>Pin Types and Conventions Used<br>Power and Ground Pins<br>SC15 I/O Power Rails<br>3.4.1 Notes on Using the SC15 I/O Power Rails<br>3.4.1.1 Power Savings Tips<br>Host Bus Interface Pins.                                                                                                                           |                                 |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6                              | Introduction<br>Pin Types and Conventions Used<br>Power and Ground Pins<br>SC15 I/O Power Rails<br>3.4.1 Notes on Using the SC15 I/O Power Rails<br>3.4.1.1 Power Savings Tips<br>Host Bus Interface Pins.<br>Video Input Pins                                                                                                       |                                 |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8                | Introduction<br>Pin Types and Conventions Used<br>Power and Ground Pins<br>SC15 I/O Power Rails<br>3.4.1 Notes on Using the SC15 I/O Power Rails<br>3.4.1.1 Power Savings Tips<br>Host Bus Interface Pins<br>Video Input Pins<br>Display Controller Interface Pins<br>Clock Pins                                                     |                                 |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9         | Introduction<br>Pin Types and Conventions Used<br>Power and Ground Pins<br>SC15 I/O Power Rails<br>3.4.1 Notes on Using the SC15 I/O Power Rails<br>3.4.1.1 Power Savings Tips<br>Host Bus Interface Pins<br>Video Input Pins<br>Display Controller Interface Pins<br>Clock Pins<br>JTAG Interface Pins                              |                                 |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8                | Introduction<br>Pin Types and Conventions Used<br>Power and Ground Pins<br>SC15 I/O Power Rails<br>3.4.1 Notes on Using the SC15 I/O Power Rails<br>3.4.1.1 Power Savings Tips<br>Host Bus Interface Pins<br>Video Input Pins<br>Display Controller Interface Pins<br>Clock Pins                                                     |                                 |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9         | Introduction<br>Pin Types and Conventions Used<br>Power and Ground Pins<br>SC15 I/O Power Rails<br>3.4.1 Notes on Using the SC15 I/O Power Rails<br>3.4.1.1 Power Savings Tips<br>Host Bus Interface Pins<br>Video Input Pins<br>Display Controller Interface Pins<br>Clock Pins<br>JTAG Interface Pins                              |                                 |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10 | Introduction<br>Pin Types and Conventions Used<br>Power and Ground Pins<br>SC15 I/O Power Rails<br>3.4.1 Notes on Using the SC15 I/O Power Rails<br>3.4.1.1 Power Savings Tips<br>Host Bus Interface Pins<br>Video Input Pins<br>Display Controller Interface Pins<br>Clock Pins<br>JTAG Interface Pins<br>External Memory Interface |                                 |

| Chapter            | 4 Sp                                                                                                                                                                                                                                         | pecifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 4-1                                                                                                                                                                                       |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.1                | SC15 Ele                                                                                                                                                                                                                                     | ectrical Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4- 1                                                                                                                                                                                        |

| 4.2                | Tempera                                                                                                                                                                                                                                      | ature Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4- 2                                                                                                                                                                                        |

| 4.3                | DC Char                                                                                                                                                                                                                                      | acteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4- 2                                                                                                                                                                                        |

|                    | 4.3.1                                                                                                                                                                                                                                        | I/O Pin DC Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-2                                                                                                                                                                                         |

|                    | 4.3.2                                                                                                                                                                                                                                        | I/O Pin Load Capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4-3                                                                                                                                                                                         |

| 4.4                | AC Char                                                                                                                                                                                                                                      | acteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4- 4                                                                                                                                                                                        |

|                    | 4.4.1                                                                                                                                                                                                                                        | Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-4                                                                                                                                                                                         |

|                    | 4.4.2                                                                                                                                                                                                                                        | Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                             |

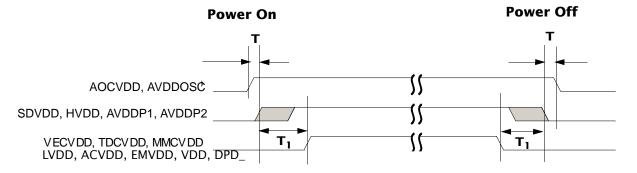

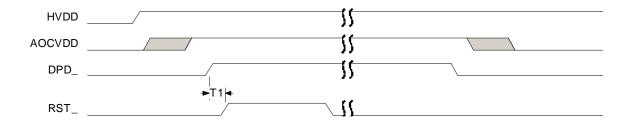

|                    | 4.4.3                                                                                                                                                                                                                                        | SC15 Power Sequencing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                             |

|                    |                                                                                                                                                                                                                                              | 4.4.3.1 Power On                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                             |

|                    |                                                                                                                                                                                                                                              | 4.4.3.2 Power Down                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                             |

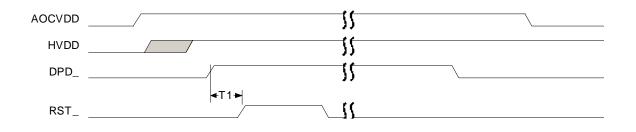

|                    |                                                                                                                                                                                                                                              | 4.4.3.3 Sequencing with DPD_ and Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                             |

|                    |                                                                                                                                                                                                                                              | <ul><li>4.4.3.4 Registers and GFSDK Function Calls for Core and IO Power Sources</li><li>4.4.3.5 Grounding Considerations</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                             |

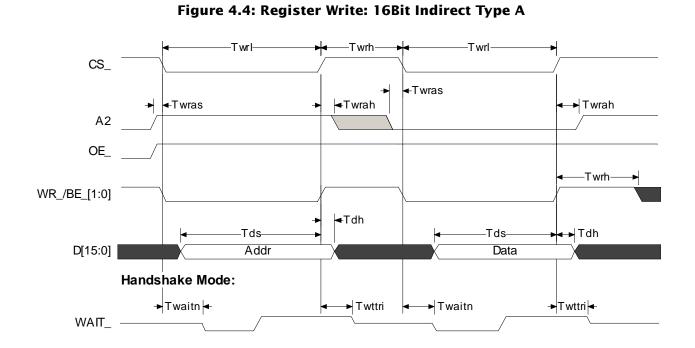

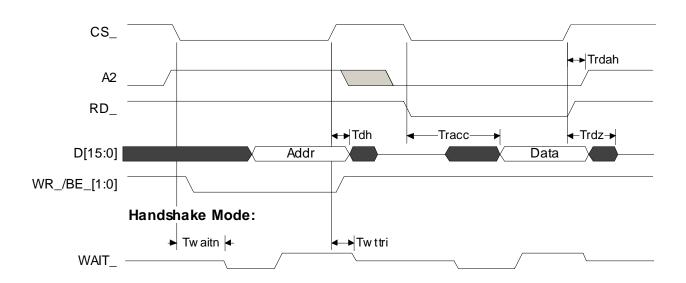

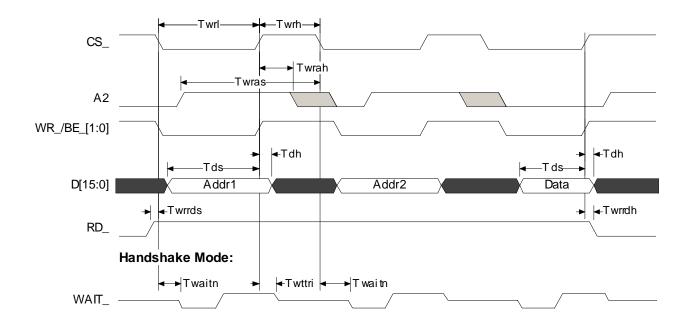

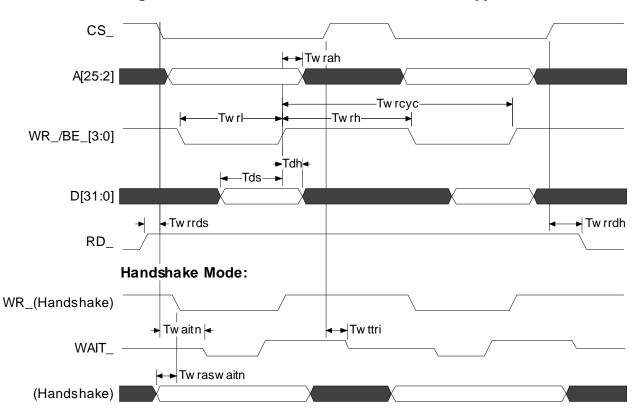

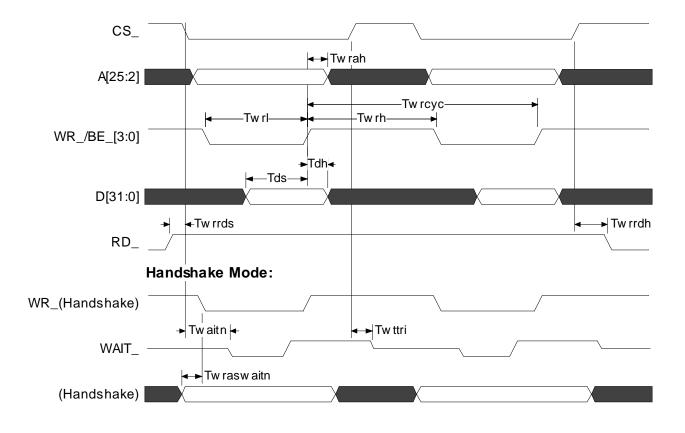

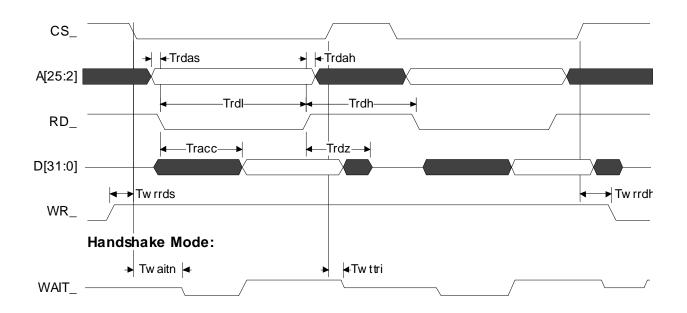

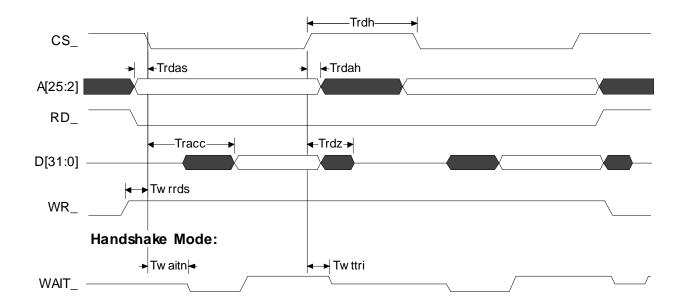

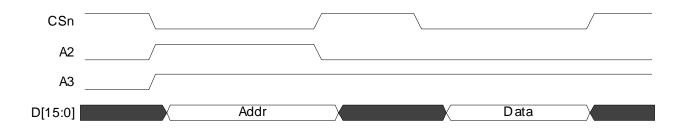

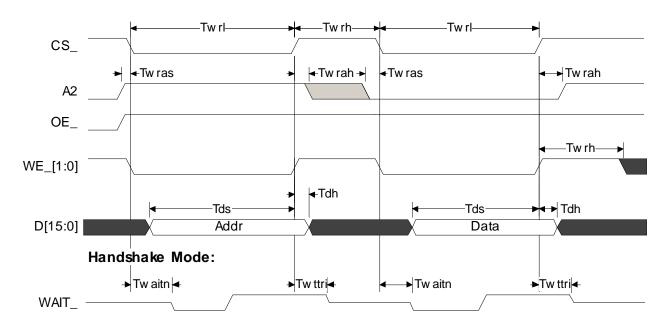

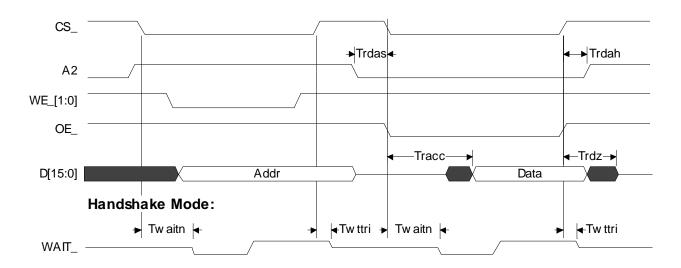

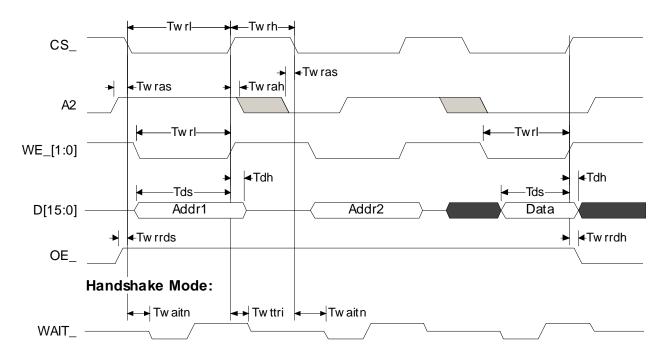

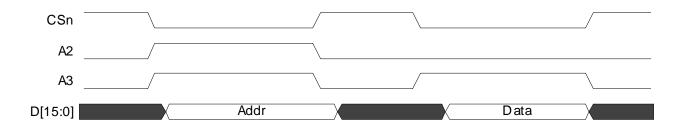

|                    | 4.4.4                                                                                                                                                                                                                                        | Host Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                             |

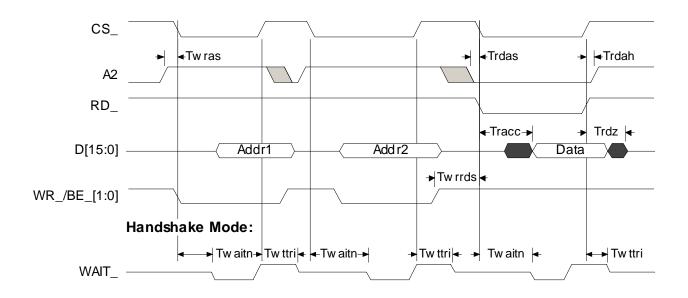

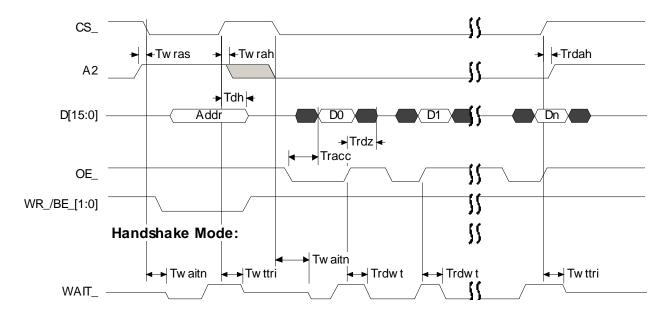

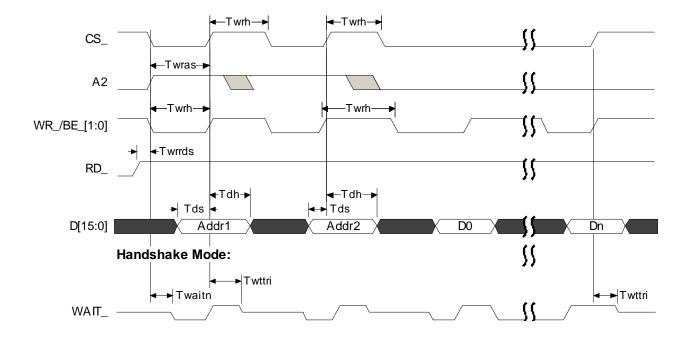

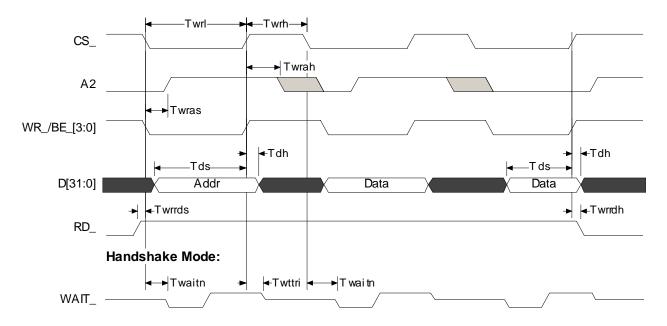

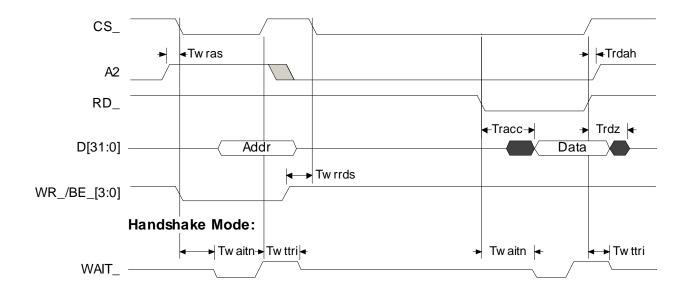

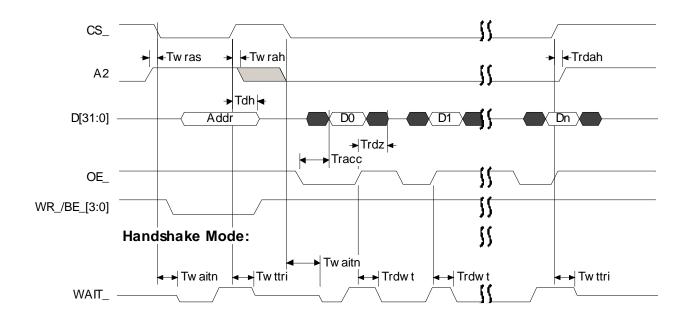

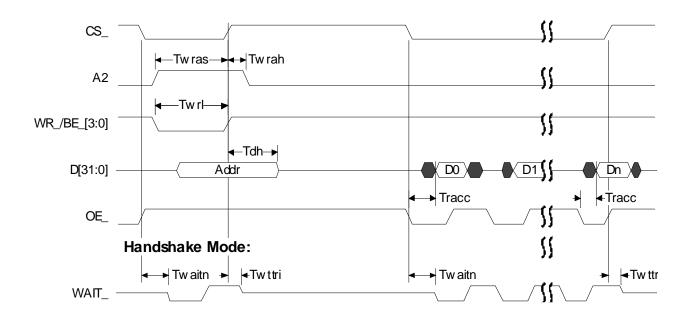

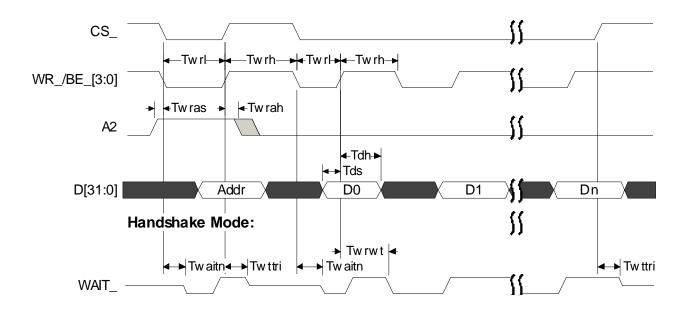

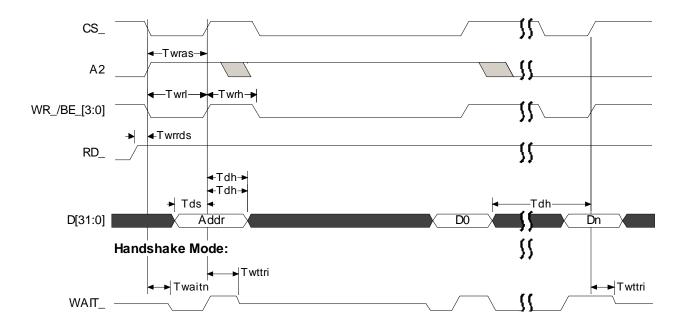

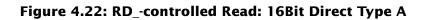

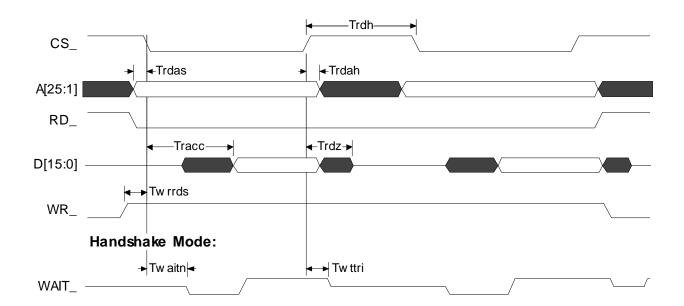

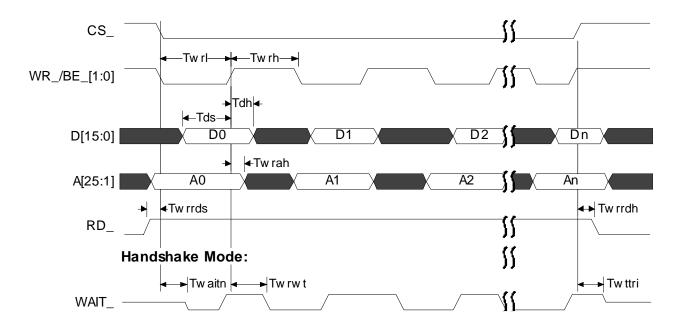

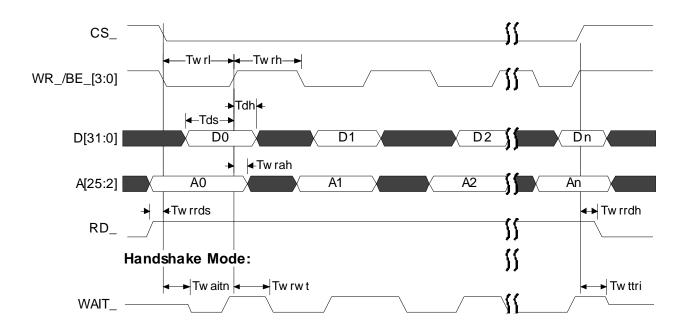

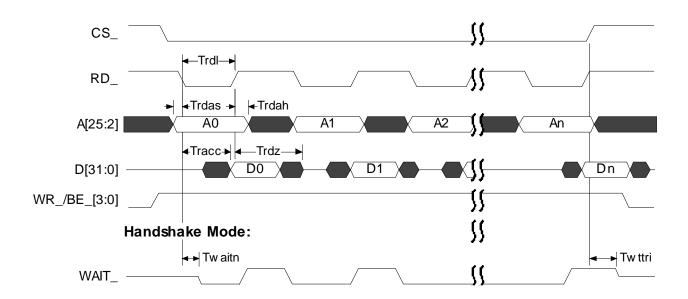

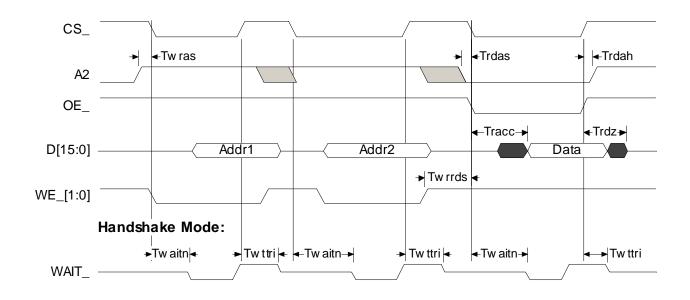

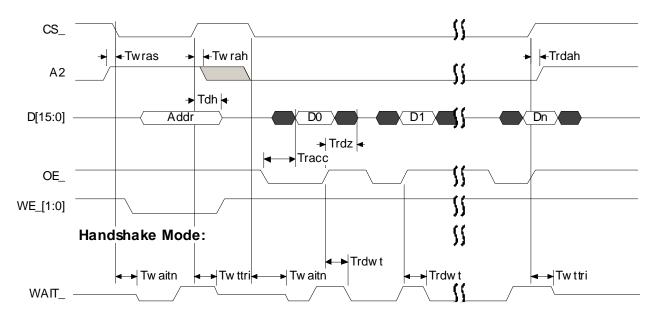

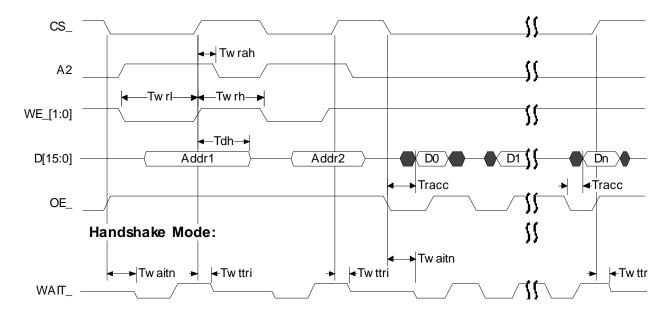

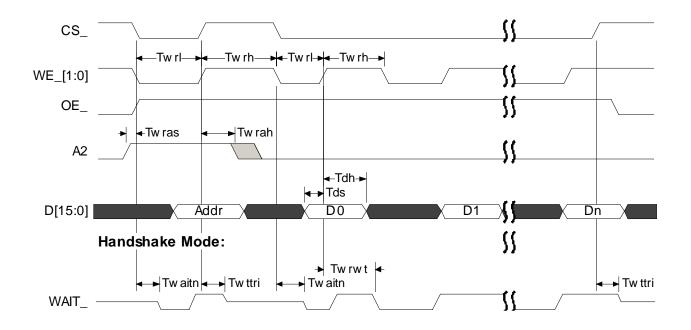

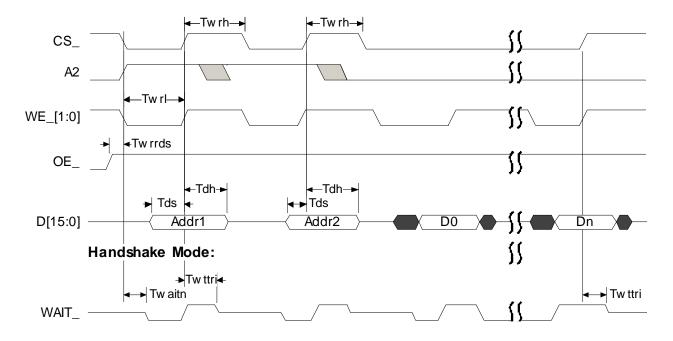

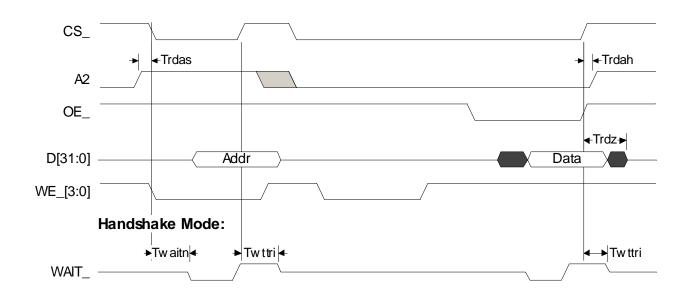

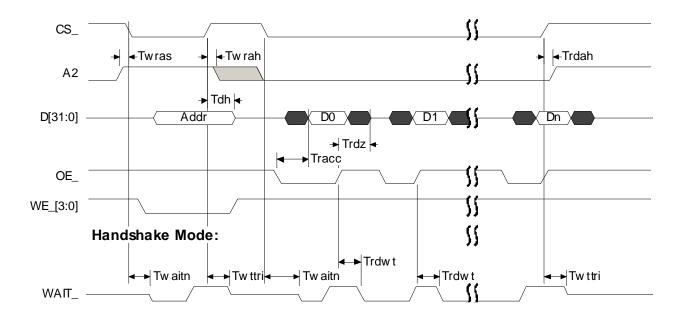

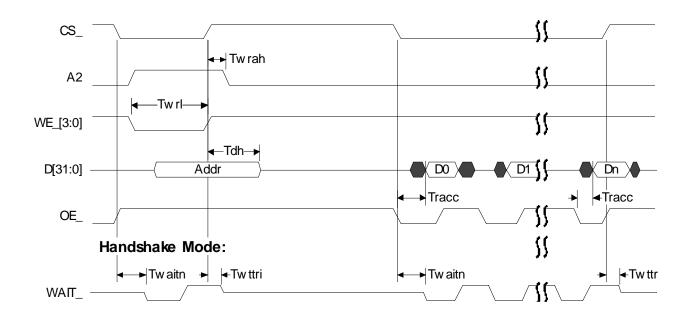

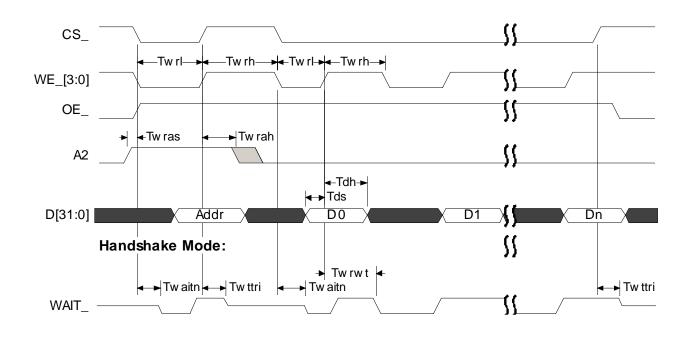

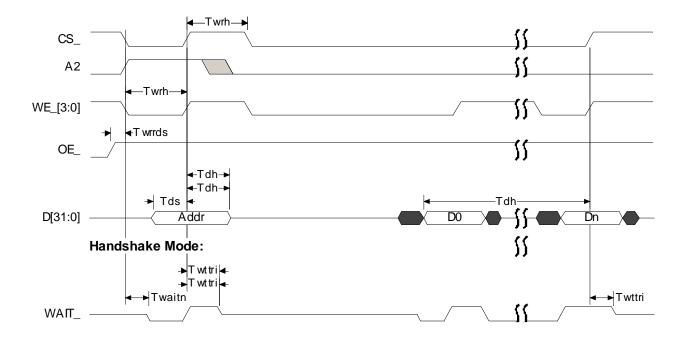

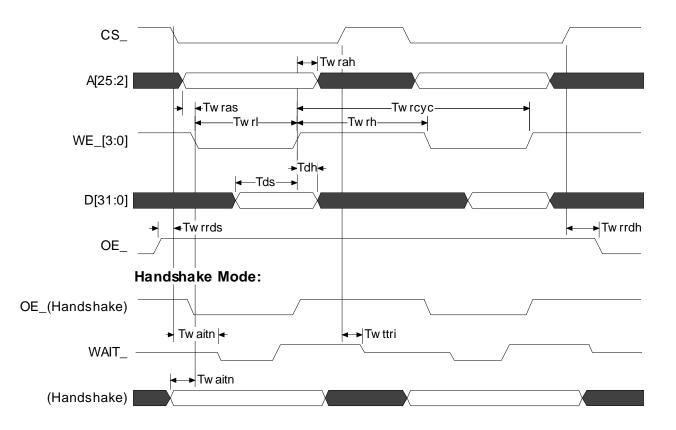

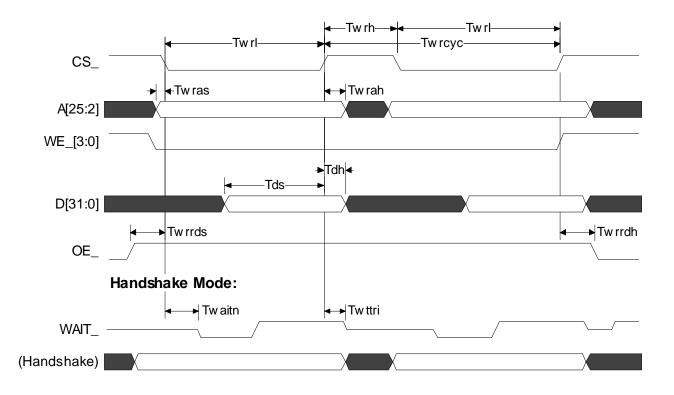

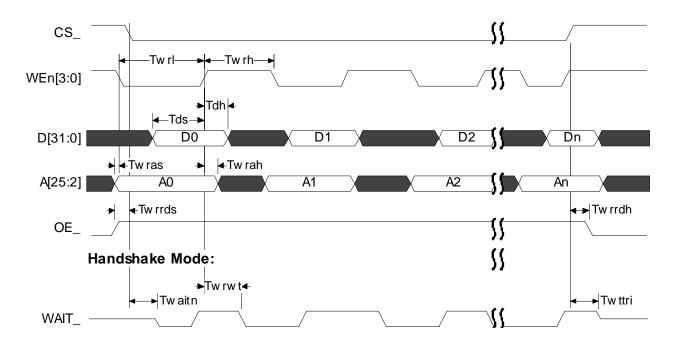

|                    | 4.4.4                                                                                                                                                                                                                                        | 4.4.4.1 Type A Host Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                             |

|                    |                                                                                                                                                                                                                                              | 4.4.4.2 Type A Host Interface Timing Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                             |

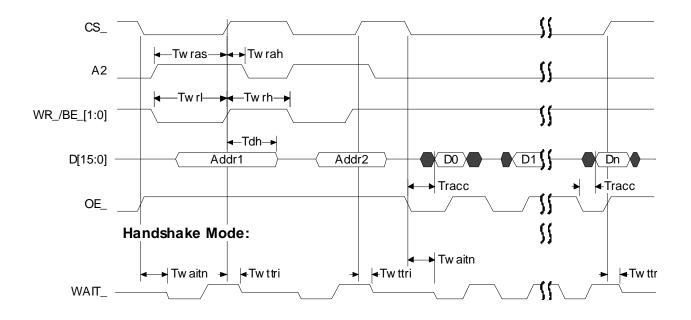

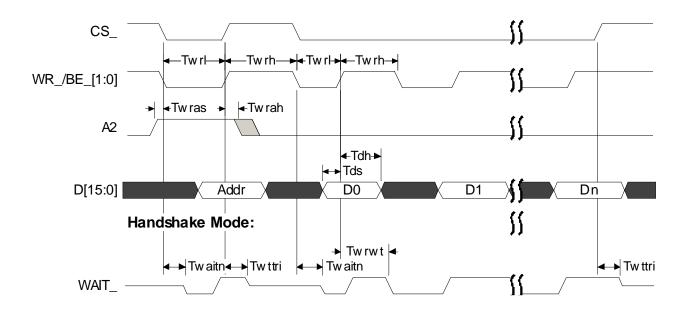

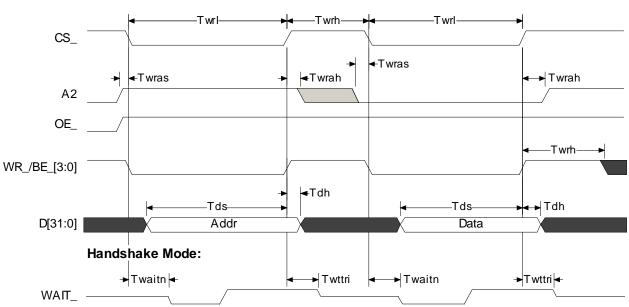

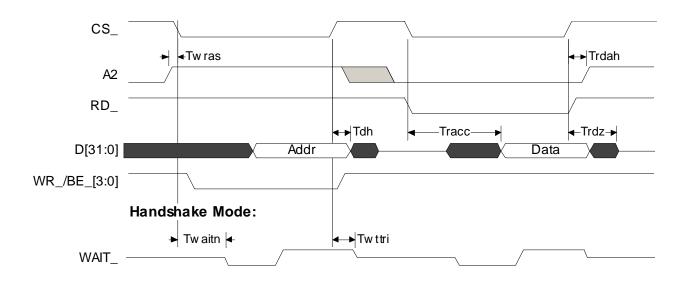

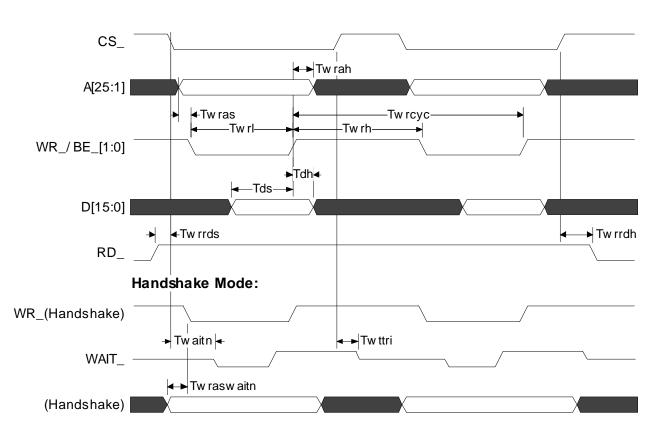

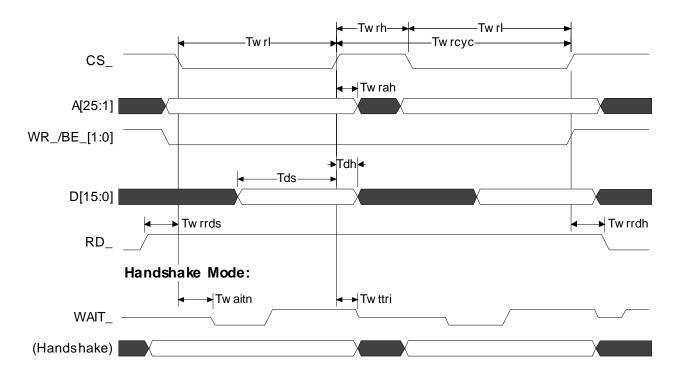

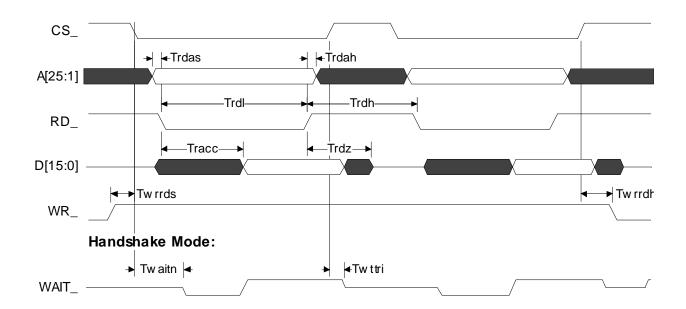

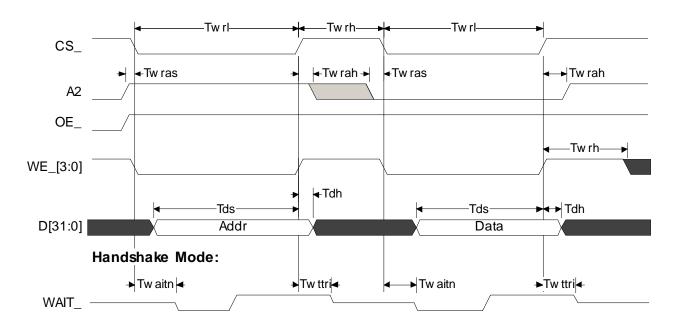

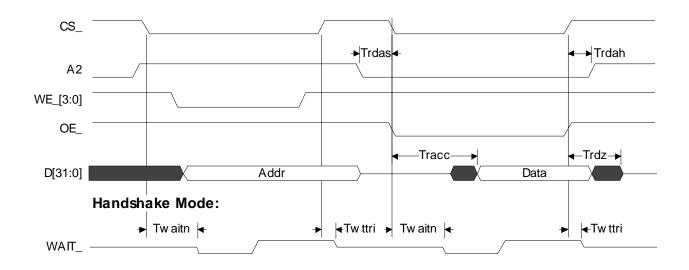

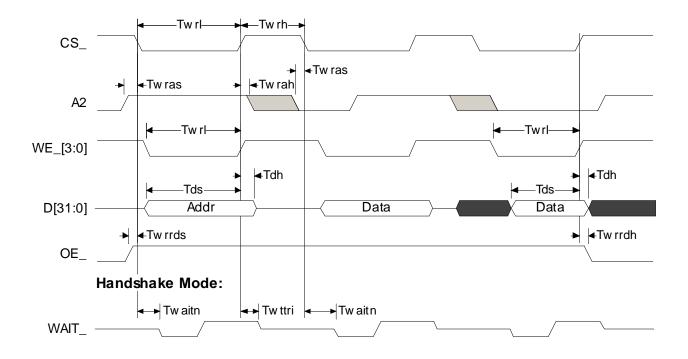

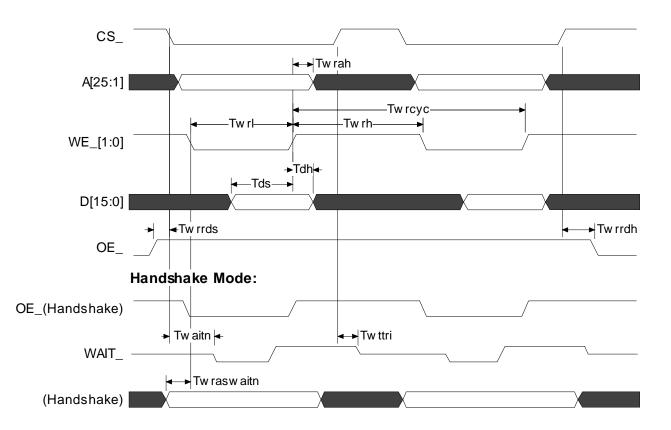

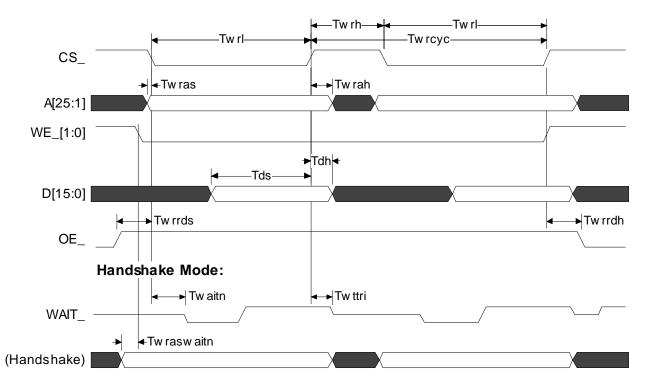

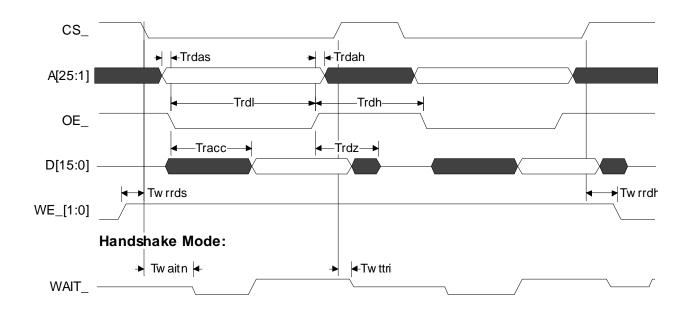

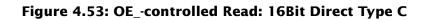

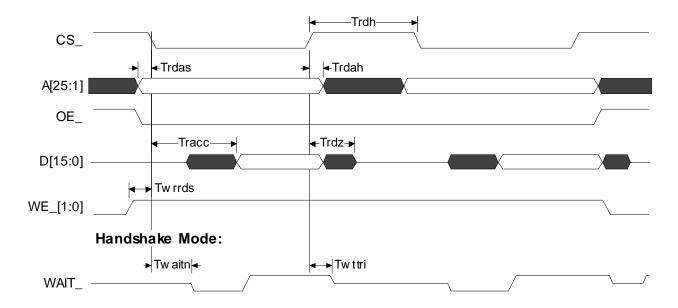

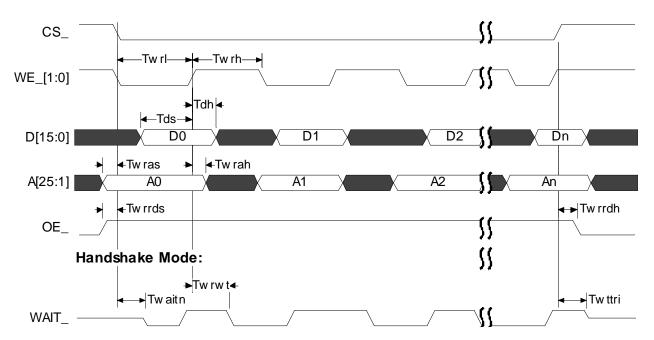

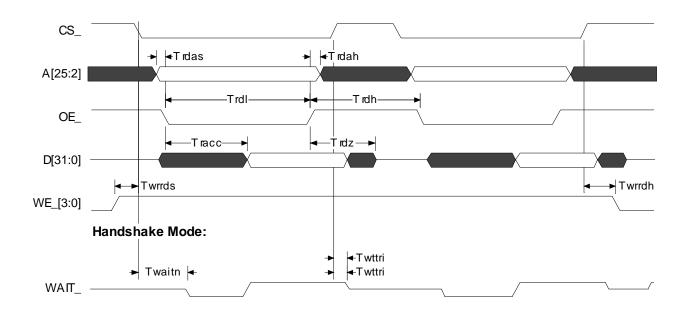

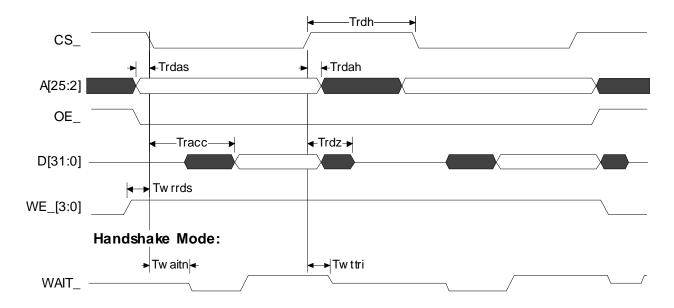

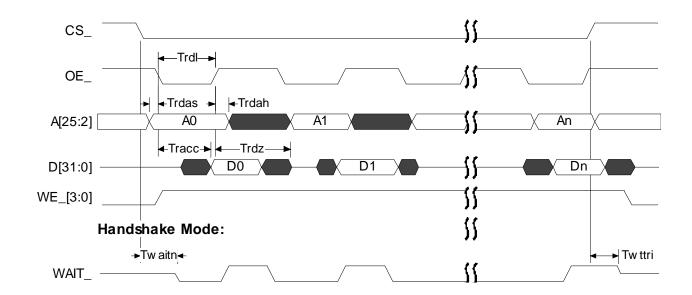

|                    |                                                                                                                                                                                                                                              | 4.4.4.3 Type C Host Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                             |

|                    |                                                                                                                                                                                                                                              | 4.4.4.4 Type C Host Interface Timing Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                             |

|                    | 4.4.5                                                                                                                                                                                                                                        | Ball Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                             |

|                    |                                                                                                                                                                                                                                              | 4.4.5.1 Ball to Signal Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                             |

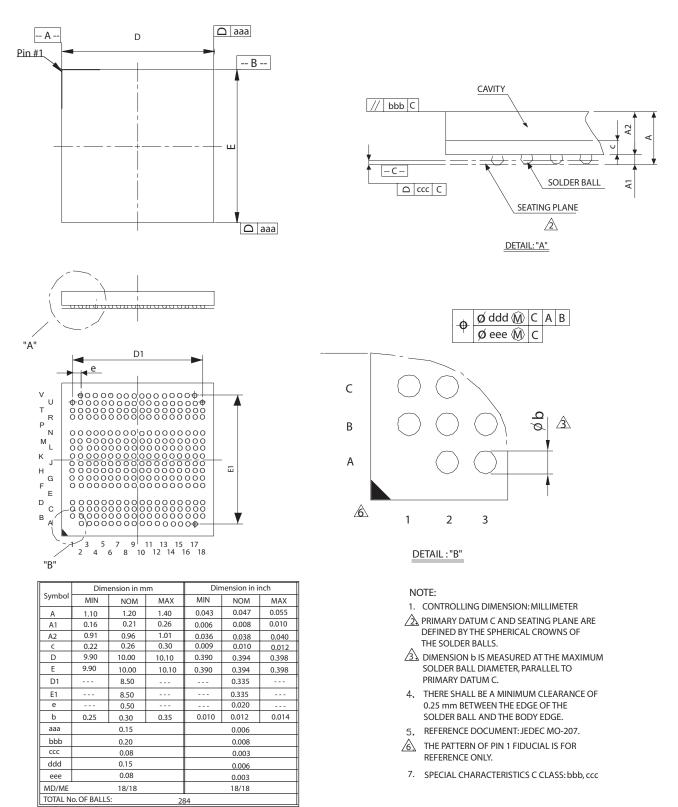

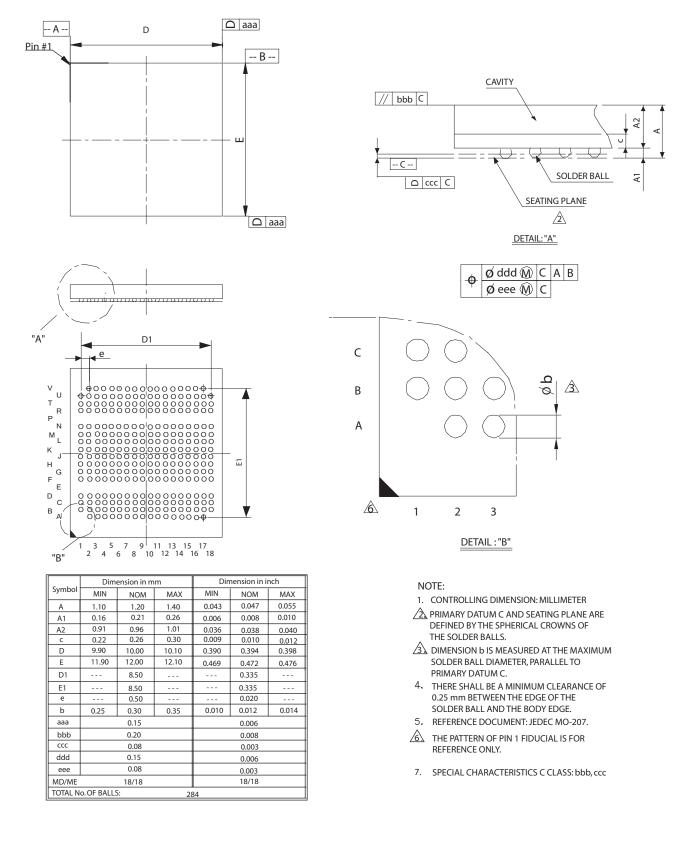

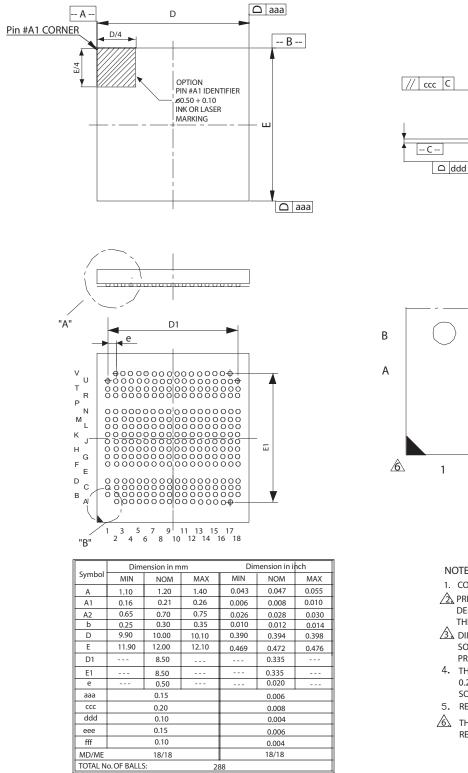

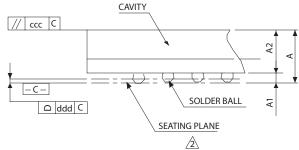

| 4.5                | Mechani                                                                                                                                                                                                                                      | cal Drawing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4- 85                                                                                                                                                                                       |

| Chapter            |                                                                                                                                                                                                                                              | emory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                             |

| Chapter<br>Chapter |                                                                                                                                                                                                                                              | egister Summary Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                             |

| -                  | 7 SC                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 7-1                                                                                                                                                                                       |

| Chapter            | 7 SC<br>Host Reg<br>HOST1X                                                                                                                                                                                                                   | gisters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>. 7-1</b><br>7- 2<br>7-2                                                                                                                                                                 |

| Chapter            | <b>7 SC</b><br>Host Ree<br>HOST1X<br>HOST1X                                                                                                                                                                                                  | gisters.<br>_ASYNC_HCONFIG1_0ASYNC_HCONFIG2_0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>. 7-1</b><br>7- 2<br>7-2<br>7-3                                                                                                                                                          |

| Chapter            | 7 SC<br>Host Reg<br>HOST1X<br>HOST1X<br>HOST1X                                                                                                                                                                                               | gisters.<br>_ASYNC_HCONFIG1_0ASYNC_HCONFIG2_0ASYNC_ADRINCREG_0ASYNC_ADRINCREG_0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>. 7-1</b><br>7- 2<br>7-2<br>7-3<br>7-4                                                                                                                                                   |

| Chapter            | 7 SC<br>Host Reg<br>HOSTIX<br>HOSTIX<br>HOSTIX<br>HOSTIX                                                                                                                                                                                     | gisters.<br>_ASYNC_HCONFIG1_0.<br>_ASYNC_HCONFIG2_0.<br>_ASYNC_ADRINCREG_0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>. 7-1</b><br>7-2<br>7-2<br>7-3<br>7-4<br>7-4                                                                                                                                             |

| Chapter            | 7 SC<br>Host Re<br>HOSTIX<br>HOSTIX<br>HOSTIX<br>HOSTIX<br>HOSTIX                                                                                                                                                                            | c15 Micro-classes<br>_ASYNC_HCONFIG1_0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>. 7-1</b><br>7-2<br>7-2<br>7-3<br>7-4<br>7-4<br>7-5                                                                                                                                      |

| Chapter            | 7 SC<br>Host Re<br>HOSTIX<br>HOSTIX<br>HOSTIX<br>HOSTIX<br>HOSTIX<br>HOSTIX                                                                                                                                                                  | c15 Micro-classes<br>_ASYNC_HCONFIG1_0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b></b> 7- 2<br>7-2<br>7-3<br>7-4<br>7-4<br>7-5<br>7-6                                                                                                                                      |

| Chapter            | 7 SC<br>Host Rea<br>HOSTIX<br>HOSTIX<br>HOSTIX<br>HOSTIX<br>HOSTIX<br>HOSTIX<br>HOSTIX                                                                                                                                                       | c15 Micro-classes<br>_ASYNC_HCONFIG1_0<br>_ASYNC_HCONFIG2_0<br>_ASYNC_ADRINCREG_0<br>_ASYNC_RDWAITREG_0<br>_ASYNC_MODEREG_0<br>_ASYNC_RSTREG_0<br>_ASYNC_RSTREG_0<br>_ASYNC_PLL1CONFIG1_0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b></b> 7-2<br>7-2<br>7-3<br>7-4<br>7-4<br>7-5<br>7-6<br>7-8                                                                                                                                |

| Chapter            | 7 SC<br>Host Rea<br>HOSTIX<br>HOSTIX<br>HOSTIX<br>HOSTIX<br>HOSTIX<br>HOSTIX<br>HOSTIX                                                                                                                                                       | c15 Micro-classes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b></b> 7-2<br>7-2<br>7-3<br>7-4<br>7-4<br>7-5<br>7-6<br>7-8<br>.7-10                                                                                                                       |